- Vhdl Code For Serial Adder Using Finite State Machine Example

- Vhdl Code For Serial Adder Using Finite State Machine Learning

A state machine is a sequential circuit that advances through a number of states. To describe a state machine in Quartus II VHDL, you can declare an enumeration type for the states, and use a Process Statement for the state register and the next-state logic.

The VHDL example shown below implements a 3-state state machine.

This state machine includes a Process Statement that is activated on every positive edge of the clk control signal for the next-state logic, and a Process Statement that is activated on a change in the state variable. This state machine has an asynchronous reset, which the Compiler recognizes.

Note: The Compiler also recognizes state machines with a synchronous reset. |

VHDL Coding of FSM: VHDL contains no formal format for finite state machines. A state machine description contains, a state variable, a clock, specification of state transitions, specification of outputs and a reset condition. The clock and reset are to be declared in a PROCESS statement. The output is specified using any concurrent statement. XST proposes a large set of templates to describe Finite State Machines (FSMs). By default, XST tries to recognize FSMs from VHDL/Verilog code, and apply several state encoding techniques (it can re-encode the user's initial encoding) to get better performance or less area. However, you can disable FSM extraction using a FSMextract d esign constraint. Register the block diagram is attached, vhdl code for serial adder using moore type fsm serial adder verilog 4 bit serial adder when doing digital system design it is very common to begin by defining how the system works with a finite state machine model this design step allows the designer to think.

The signal state stores the current state of the state machine. The declaration of the type STATE_TYPE defines the states s0, s1, and s2 for state_machine.

At startup, the state machine is initialized to the reset state. If there is no reset state, the state machine is initialized to the first state in the Type Declaration. Otherwise, the first Case Statement determines the transitions between the states (that is, which state to enter on the next rising edge of clk) and the second Case Statement determines the value of the outputs for each state.

The Compiler recognizes state machines and reports them as such in the State Machines section of the Report window only if all of the following conditions are met:

The type of the signal or variable that represents the state machine must be an enumerated type.

The Process Statement that describes the state machine must be clocked, and must contain an If Statement that checks for a positive edge of the

clkcontrol signal.The state machine behavior, that is, the next-state logic, is defined with Case Statements at the top level.

All assignments to the signal or variable that represents the state machine are within the process.

The state machine must have more than two states.

VHDL state machines that do not meet these conditions are converted into logic gates and registers that are not listed as state machines in the Report window. The Compiler also converts VHDL state machines to 'regular' logic when the ENUM_ENCODING attribute is used to manually specify state assignments in a project.

Note: Because the Compiler usually produces the best results, Altera recommends that you do not use the |

You can assign states in the following ways:

For more information, refer to the following sections of the IEEE Std 1076-1993 IEEE Standard VHDL Language Reference Manual:

Section 8.1: Wait Statement Barcode plugin for illustrator.

Section 8.6: If Statement

Section 8.7: Case Statement

Section 9.2: Process Statement

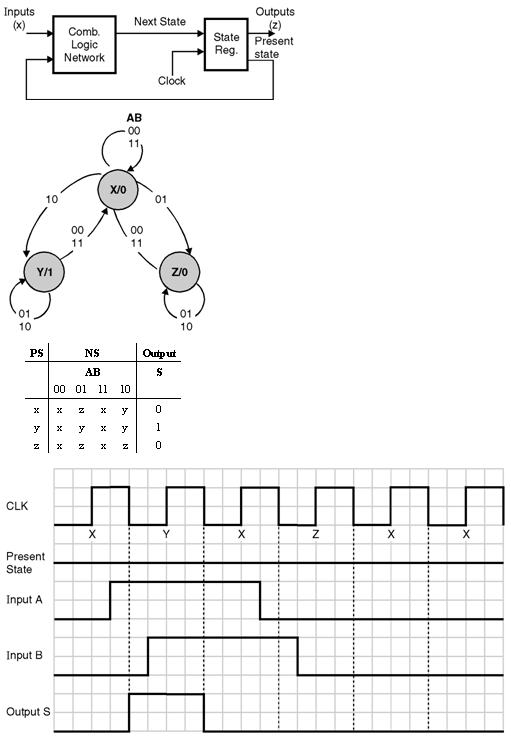

The serial adder is a digital circuit in which bits are added a pair at a time.

Let A and B be two unsigned numbers to be added to produce Sum = A + B. In this we are using three shift registers which are used to hold A, B and Sum. Now in each clock cycle, a pair of bits is added by the adder FSM and at the end of the cycle, the resulting sum is shifted into the Sum register.

Mealy type FSM for serial adder:

Let G and H denote the states where the carry-in-values are 0 and 1. Output value s depends on both the state and the present value of inputs a and b.

In state G and H:

Vhdl Code For Serial Adder Using Finite State Machine Example

| Input valuation | Output (s) | State |

|---|---|---|

| 00 | 0 | FSM will remain in same state G |

| 01,10 | 1 | FSM will remain in same state G |

| 11 | 0 | FSM moves to state H |

| 01,10 | 0 | FSM will remain in same state H |

| 11 | 1 | FSM will remain in same state H |

| 00 | 1 | FSM moves to state G |

A single Flip-Flop is needed to represent the two states. The next state and output equations are:

Pirate poppers download torrent fifa 19. Y = ab + ay + by

s = a ⊕ b ⊕ y

The flip-flop can be cleared by the Reset signal at the start of the addition operation.

Moore type FSM for serial adder:

In a Moore type FSM, output depends only on the present state. Since in both states, G and H, it is possible to produce two different outputs depending on the valuations of the inputs a and b, a Moore type FSM will need more than two states. Therefore we will four states namely: G0, G1, H0 and H1.

The next state and output equations are:

Y1 = a ⊕ b ⊕ y2

Y2 = ab + by2 + by2

s = y1

The flip-flop can be cleared by the Reset signal at the start of the addition operation.

Moore type FSM for serial adder:

In a Moore type FSM, output depends only on the present state. Since in both states, G and H, it is possible to produce two different outputs depending on the valuations of the inputs a and b, a Moore type FSM will need more than two states. Therefore we will four states namely: G0, G1, H0 and H1.

The next state and output equations are:

Y1 = a ⊕ b ⊕ y2

Y2 = ab + by2 + by2

s = y1

The only difference between circuits of Mealy and Moore type FSM for serial adder is that in Moore type FSM circuit, output signal s is passed through an extra flip-flop and thus delayed by one clock cycle with respect to the Mealy type FSM circuit.

Vhdl Code For Serial Adder Using Finite State Machine Learning

References: Fundamentals of Digital Logic with VHDL Design